Counters

A counter is a device to determine the number of elements of a finite set. The modulus of a counter is the number of the states that it can count.

As learned in Chapter 7, flip-flops (FF) can be connected to perform counting operations, and counters,according to the way the FFs are clocked, are classified into two broad categories:

- Asynchronous counters(异步计数器)根据上一个 FF 的提示,选择改变自身的状态。

- Synchronous counters(同步计数器)每一个时钟信号发出时,根据之前电路的状态,综合判断是否改变状态。

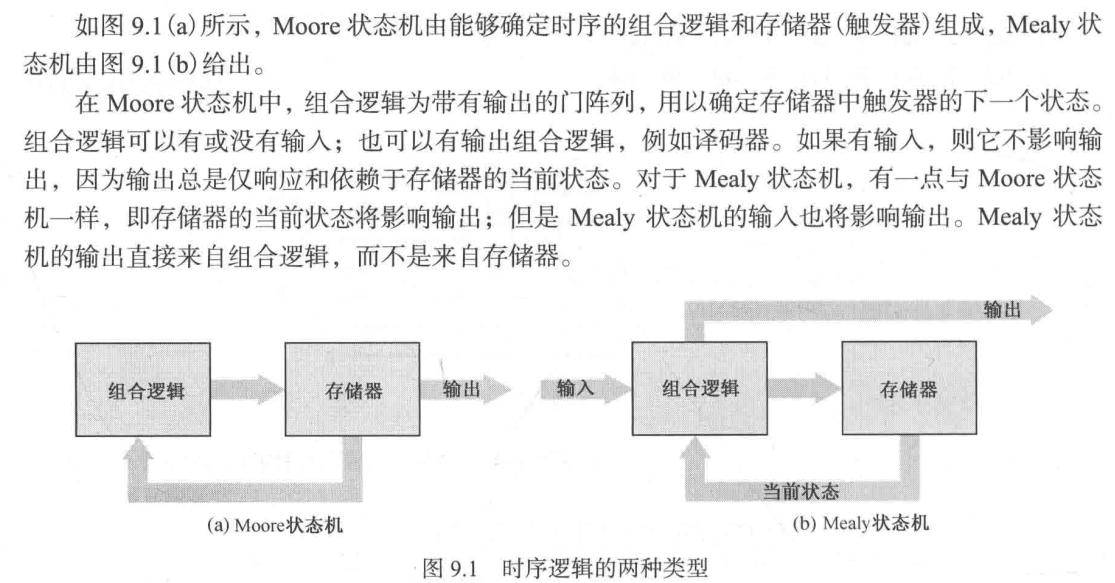

Finite State Machine (有限状态机)

A state machine (有限状态机) is a sequential circuit that has a finite number of states occurring in a prescribed order.

E.g., a counter is a typical example of a state machine, and its number of states is the modulus.

有限状态机的一般模式

输入可以是 Enable,Load 等等,参见 74HC163。

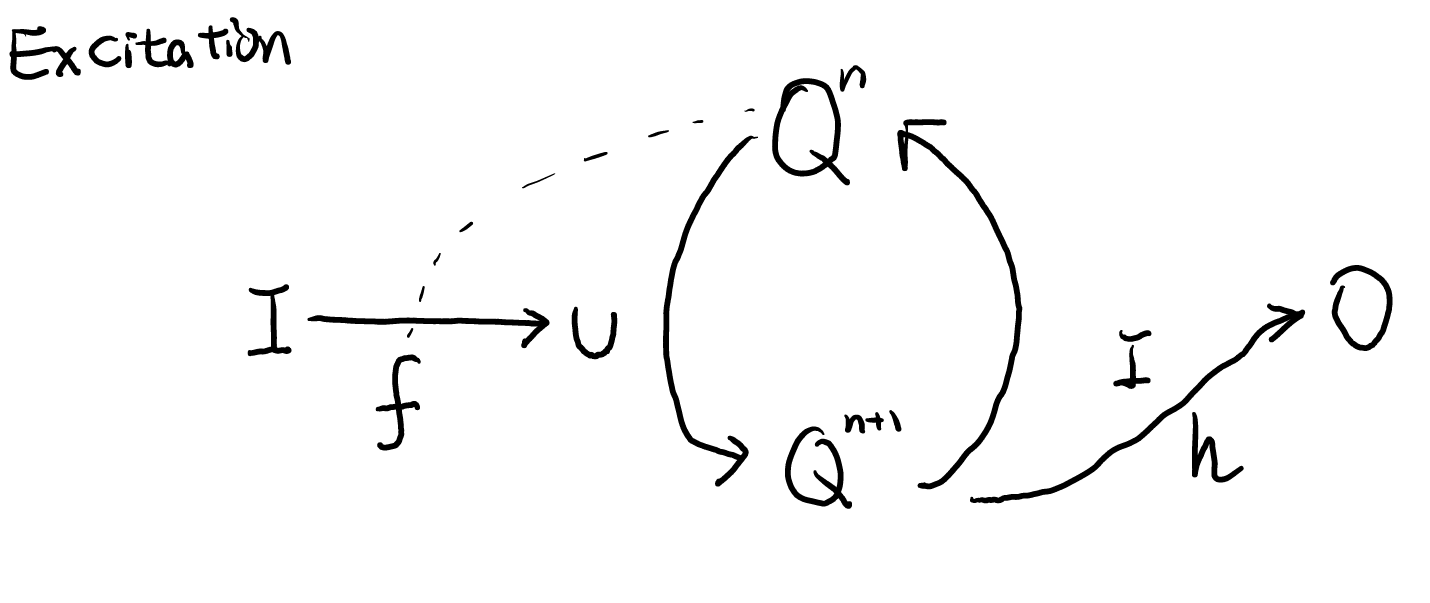

**Analysis: ** Derive a behavior model for a given circuit.

- Excitation Equation (激励方程/驱动方程)

- Characteristic equation (特性方程):

- Output Equation (输出方程)

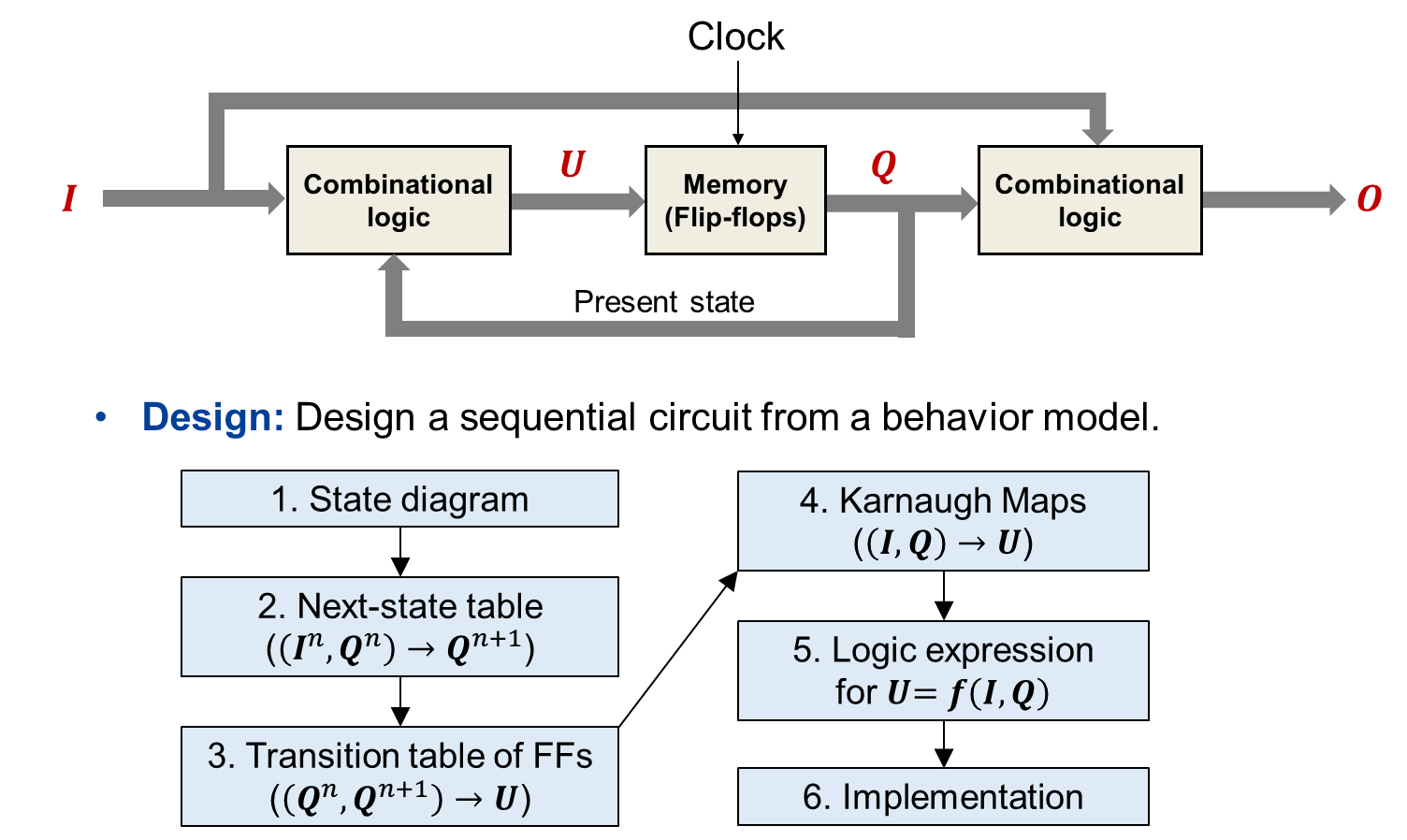

Design: Design a sequential circuit from a behavior model.

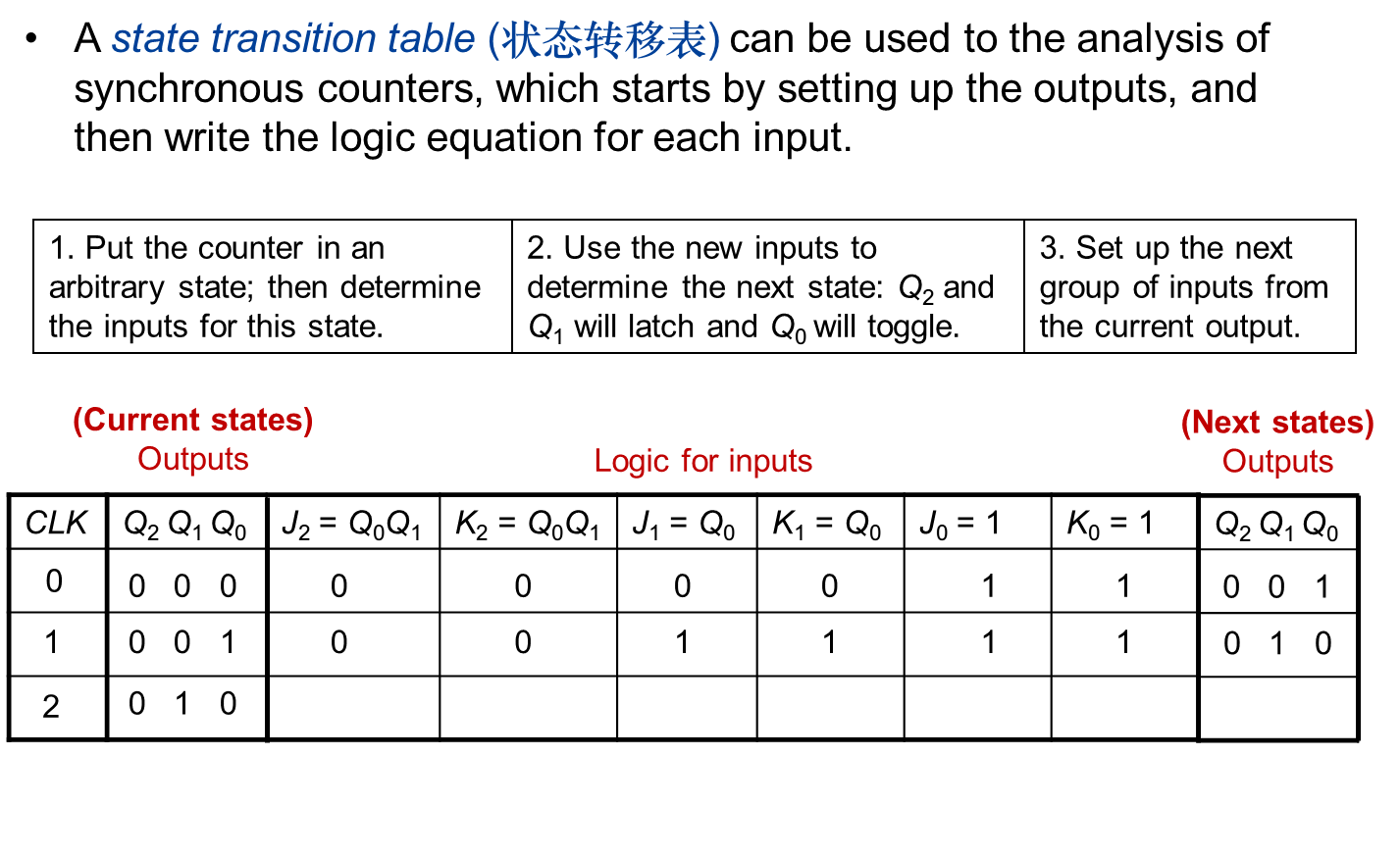

Analysis of Synchronous Sequential Circuits

J-K flip-flops

| 0 | 0 | 0/1 | |

| 1 | 0 | 0/1 | 1 |

| 0 | 1 | 0/1 | 0 |

| 1 | 1 | 0/1 |

D flip-flops

S-R latches

Design of Synchronous Sequential Circuits

Asynchronous Counters (异步计数器)

3-Bit Asynchronous Counters(三比特异步计数器)

注意是正边沿触发,因此,检测的是 等等。

下降沿触发。两者的输出(经过时间平移之后)是一样的,但是中间的实现方式不同,需要注意都是用上升沿触发或者都是用下降沿触发。

Toggle mode D FFs: connect to .

Propagation Delay

If the edge-triggered J-K FFs have a a propagation delay of 10 ns, then, the maximum frequency of Clock

f_\max=1/T_\min=1/30 \mathrm{~ns}=33.3\mathrm{~MHz}

Asynchronous Decade Counters(异步十进制计数器)

An -bit counter can be designed to have a modulus less than , and the resulting sequence is called a truncated sequence. 如何进行截断?到达特殊状态清零即可。使用 JK 触发器的异步清零功能。

A decade counter involves a sequence of 0000 through 1001.

只要 ,,就可以清零。这种方法称为部分编码。

Glitch:毛刺,假信号。到达 状态时,清零信号还未传递,因此会出现 Glitch.

需要检测第一个不合法的位置,例如,12-based counter 中 1-11 是合法状态,因此需要检测 12 这个状态,在这里,只要 就可以判断是 12 这个状态,然后复位也是只用复位这两位。

74LS93A

74LS93A is an example of an IC asynchronous counter. It has one independent toggle J-K FF driven by CLK A, and three toggle J-K FFs that form a 3-bit asynchronous counter driven by CLK B.

注意 和 相连接。

异步清零 需要 同时等于 HIGH. 检测状态 .

Synchronous Counters (同步计数器)

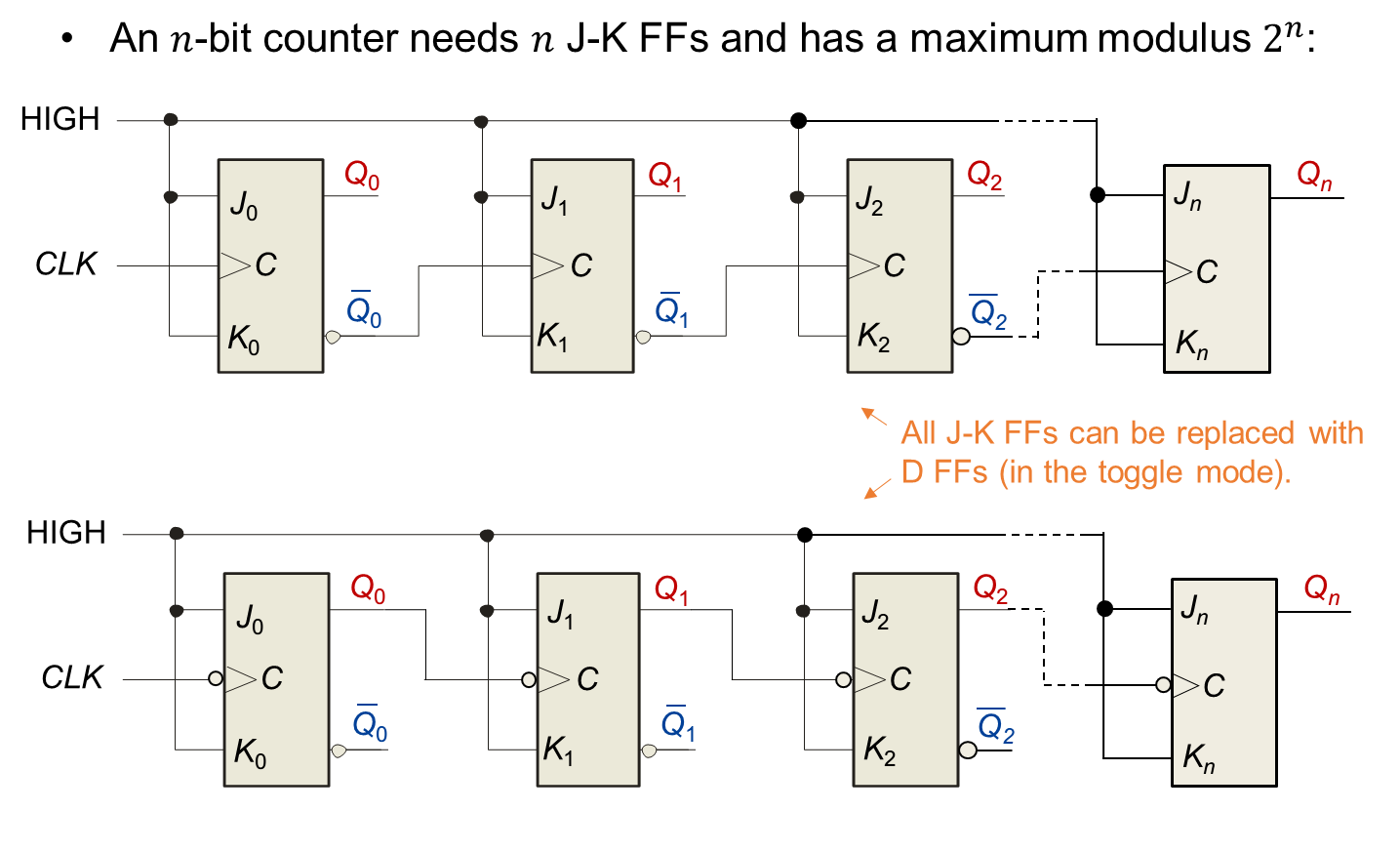

In a synchronous counter, all flip-flops are clocked together with a common clock pulse.

Synchronous counters overcome the disadvantage of accumulated propagation delays of the asynchronous ones, but generally they require more circuitry to control state changes.

在同步计数器中,所有的触发器都是用一个共同的时钟脉冲进行时钟连接。

同步计数器克服了异步计数器的累积传播延迟的缺点,但通常它们需要更多的电路来控制状态变化。

2 Bit Synchronous Counter

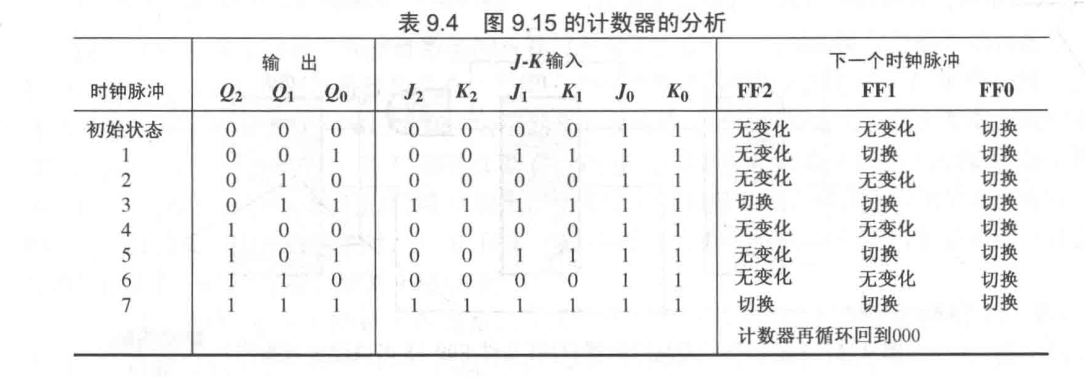

3-Bit Synchronous Binary Counters

4 bit Synchronous Counter

模拟进位

按照常理, 下一个应该是 ,这里要把他变为 ,因此我们第一需要添加特判 ,这时对第三位进行翻转操作,而且当 时不能翻转 ,因此又需要一个特判。

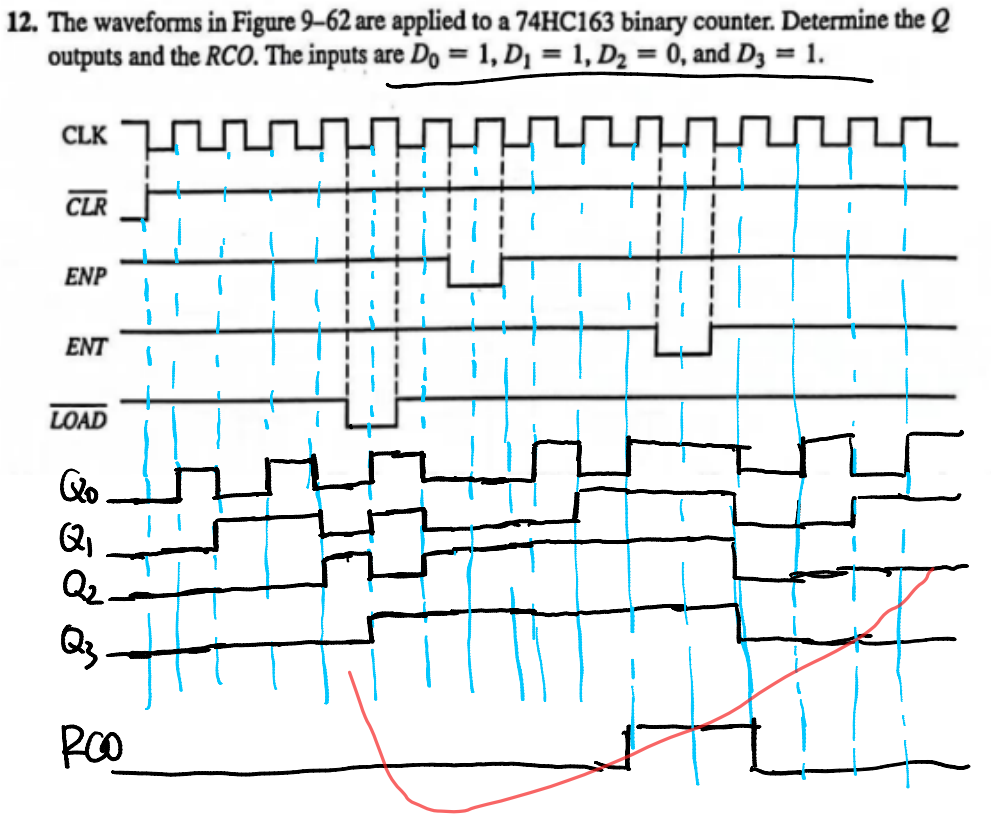

74HC163

74HC163: 4-bit synchronous binary counter. Features:

- Data inputs

- ENT/ENP to enable

- synchronous clear.

- synchronous set.

Inhibit:禁止工作,当 里面有一个是 0 时。输出状态保持不变。

注意:只有当时钟信号上升时,才会触发数据输出的状态改变。 如果要串联计数器,需要将 RCO 连到下一个计数器的 CLK 信号上,并且让 RCO 与 CLR 连接,以便于清零。

E.g., use 74HC163 to realize a counter with a modulus of 12.

74HC160

Synchronous BCD decade counter.

同步置数:跟着时钟信号,异步清零,只要 就代表立马清零。

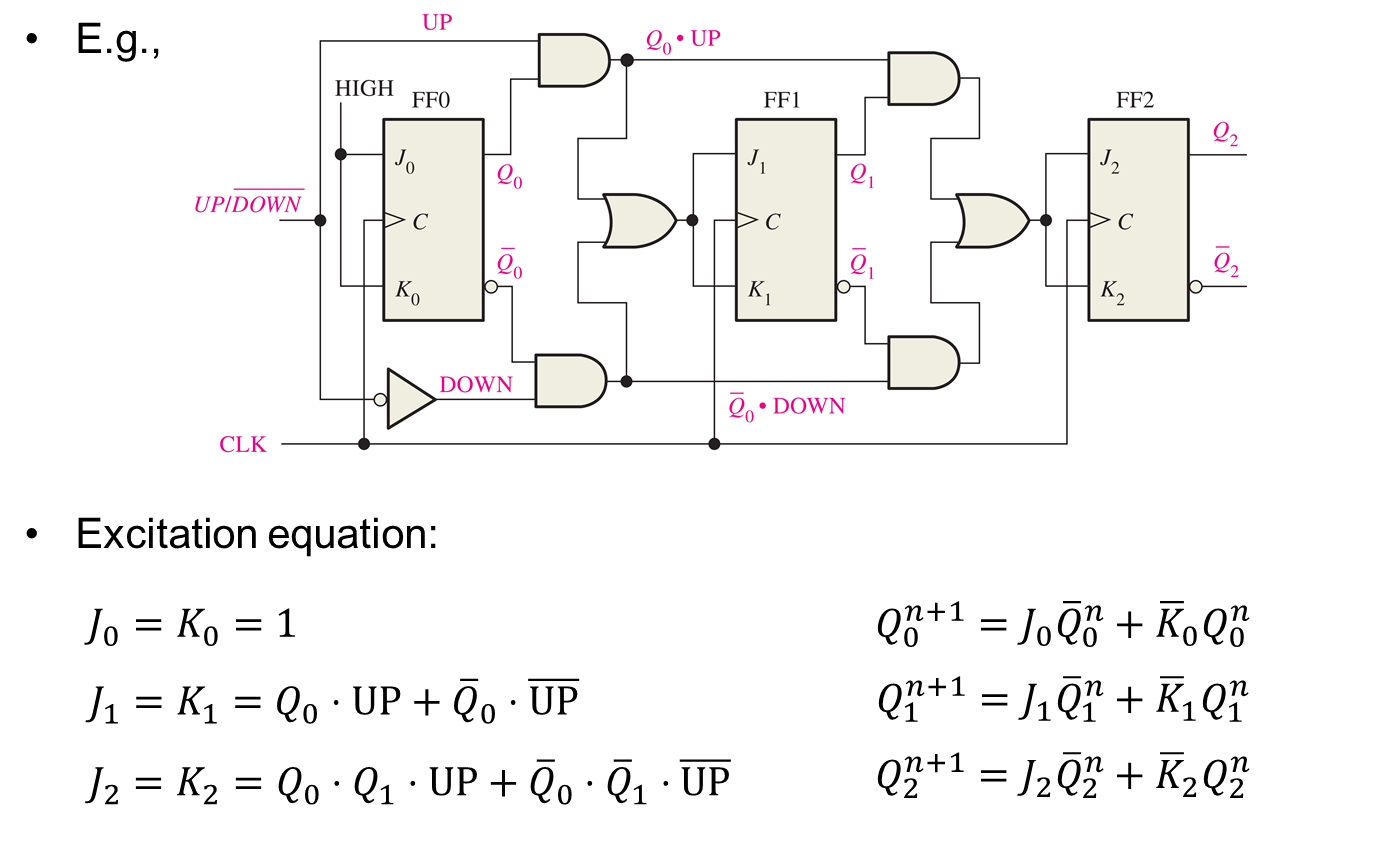

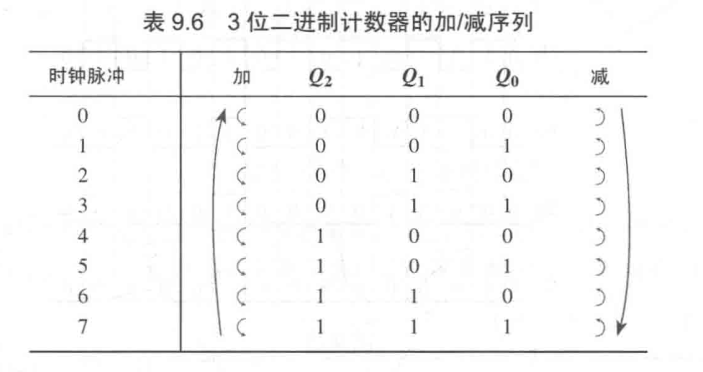

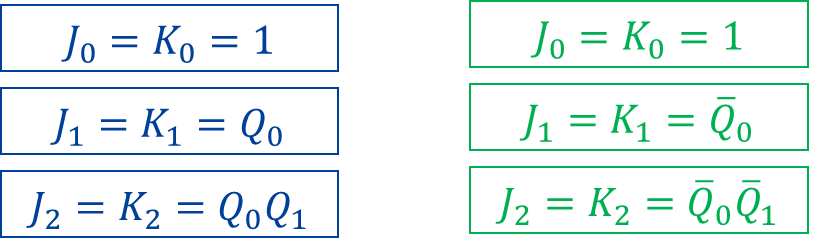

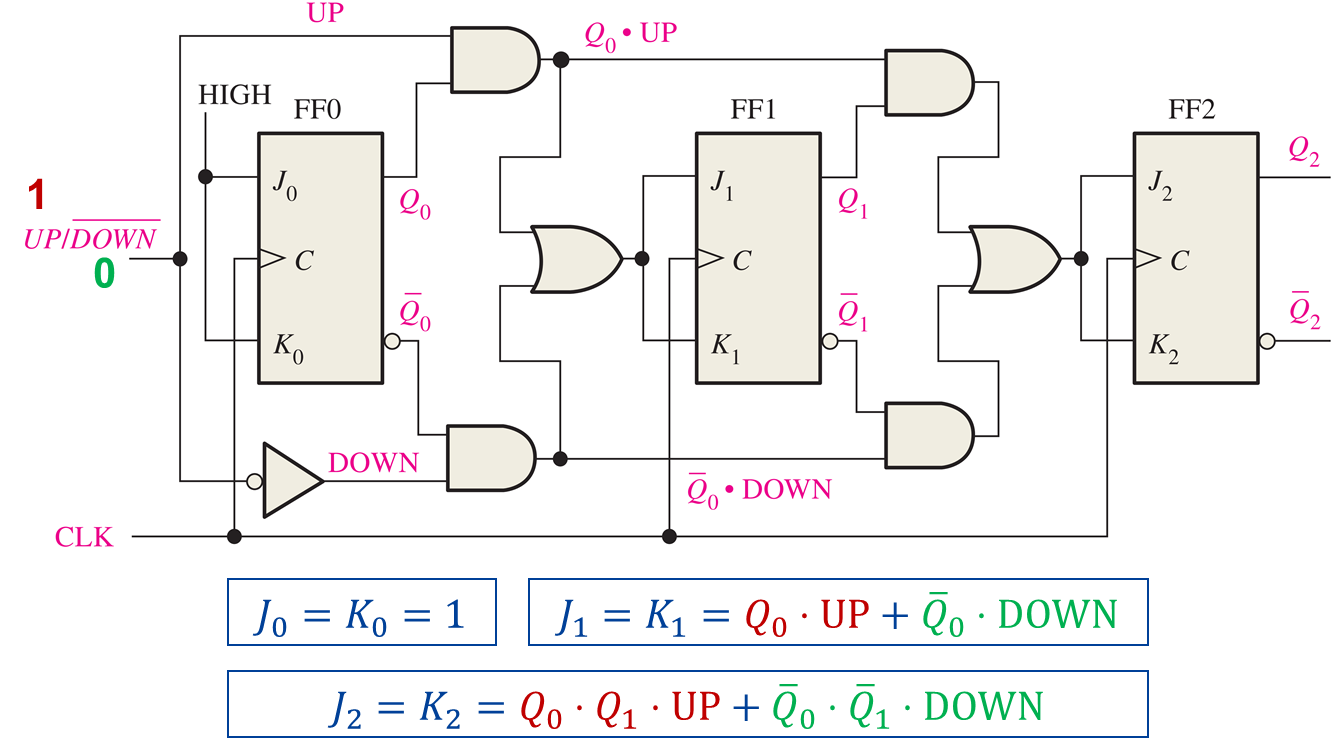

加/减同步计数器 Up/Down Synchronous Counters

Conditions for flip-flop toggling in the up and down counters.

注意观察 的表达,。

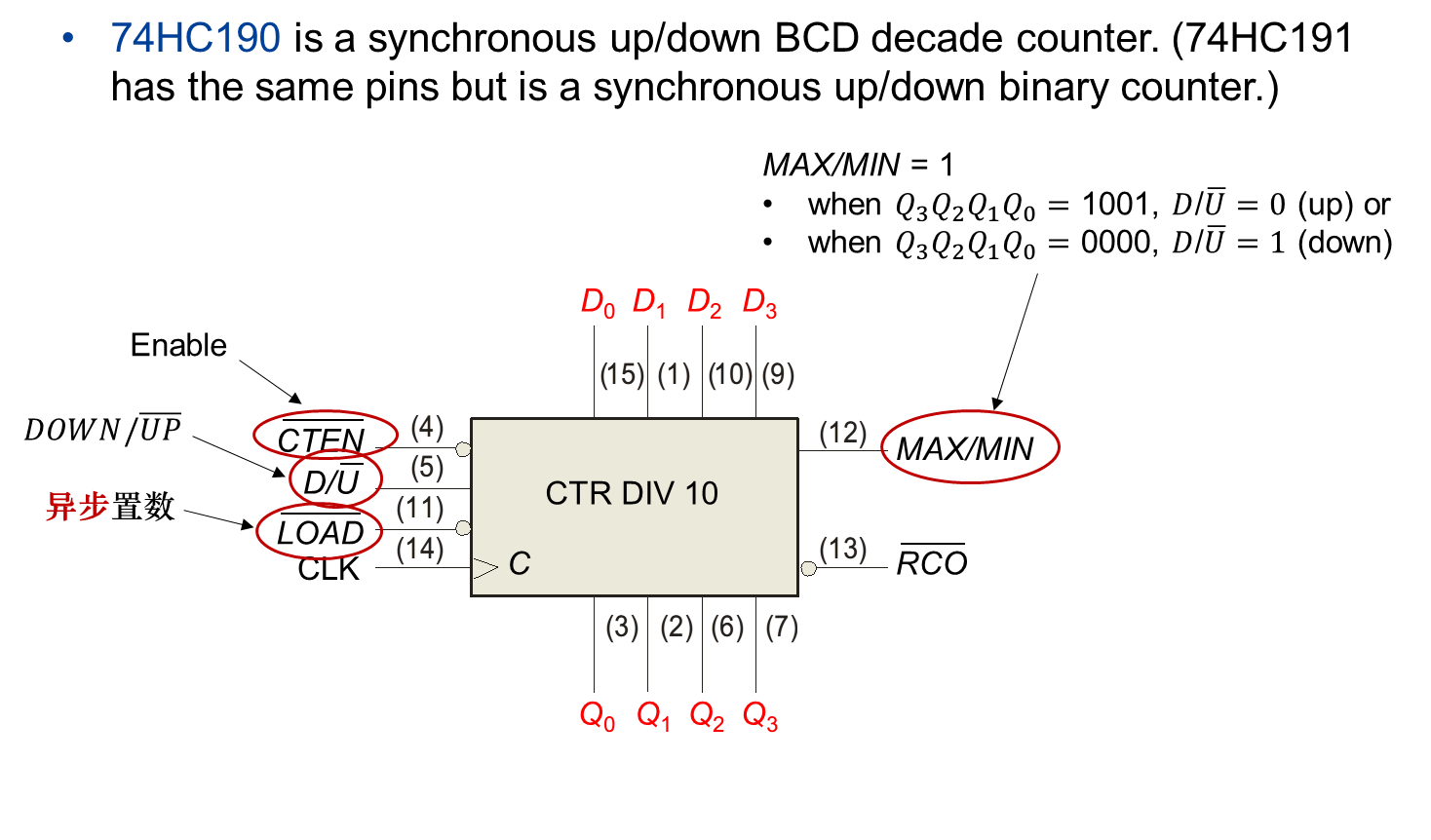

74HC190/74HC191

MAX/MIN 常常用于级联计数器,若 ,代表 Up, 进位,若 ,代表 Down, 借位。

Design of Synchronous Counters(同步计数器设计)

Design of Synchronous Sequential Circuits

-

State Diagram

-

Next-state Table

-

Transition Table of FFs

-

Karnaugh Maps

-

Logic Expression for

-

Implementation

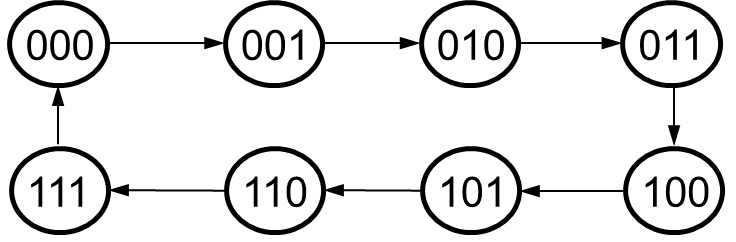

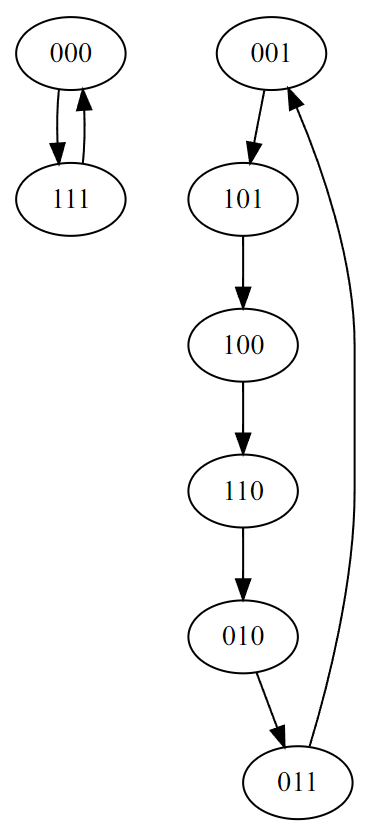

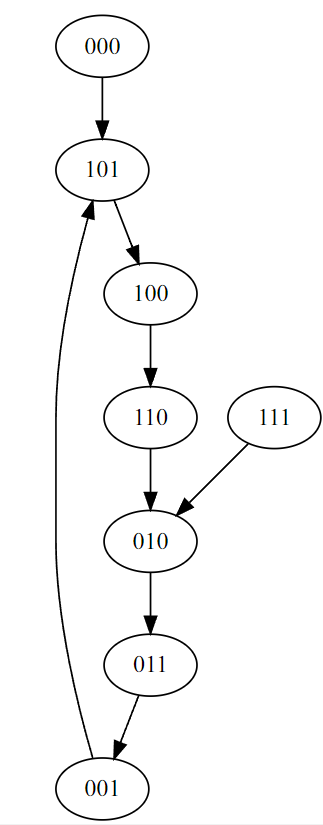

Example: Design a 3-bit Gray code counter

(1). State Diagram

(2). Next-state table

(3). Transition Table of a J-K FF

相反的,枚举所有可能的输入。

(4) Karnaugh Maps

(5). Logic expression for

(6). Implementation

Implement the expressions with combinational logic, and combine with the flip-flops to create the counter.

Example: Design a counter with the binary count sequence shown in the state diagram. Use D flip-flops.

7.Analyze the design

是否能够自启动

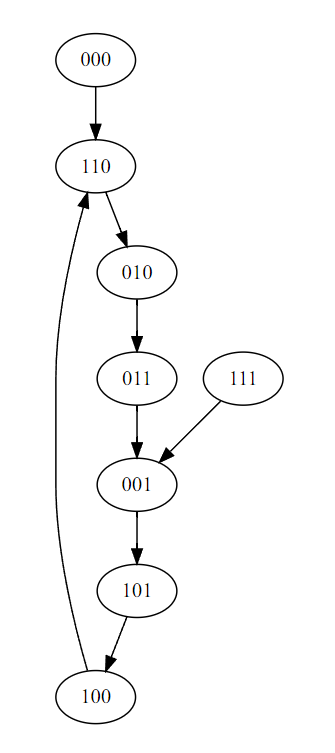

Example Design a 3 bit up/down counter with Gray code Sequence.

An Example with Auto Start (Re-) Design

数字控制装置中常用的步进电动机有 A, B, C三个绕组. 电动机运行时要求三个绕组以 A → AB → B → BC → C → CA → A的顺序循环通电. 试设计一个电路实现之。

本任务所需计数器模数为6, 所以触发器的个数应(至少)为3. 我们选用3个J-K触发器.

用三个触发器的输出端 分别控制电动机的三个绕组A, B, C, 并以“1”表示通电, “0”表示不通电。以为 序排列:

无关状态以红色表示。

需要让无效的状态到有效的状态。

强制设为 1.

1111 -> 0010

能不能自启动,需要每一个状态都能走入循环。

Cascaded Counters (级联计数器)

Counter cascading means that the last-stage output of one counter drives the input of the next counter, which can be used to achieve higher-modulus operation.

Asynchronous cascading: The output of a lower-order counter is properly connected to the clock of the next higher-order counter.

上升沿触发的。

Asynchronous cascading has high latencies.

Synchronous cascading: The terminal count (e.g., TC, RCO) of a counter is properly connected to the enable (e.g., EN, CTEN) of the next higher-order counter. (All counters have the same clock input.)

利用延迟,就可以检测到 TC,发现了前面的计数器已经走过了一个循环。

需要全部接上。

E.g., the following shows two 74HC190 (up/down decade counter) connected in the UP mode as a cascaded counter with modulus 100.

Example Determine the frequency of for the two 74HC190 in Page 7.

| 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

Cascaded Counters with Truncated Sequences

The previous cascading leads to full-modulus cascading, i.e., the overall modulus is equal to the product of the individual modulus.

A truncated sequence with cascaded counters can be implemented:

跳过 的数。

Counter Decoding (计数器译码)

Counter decoding involves using decoders or logic gates to determine when the counter is in a certain binary state in its sequence.

Propagation delays of counters (in particular asynchronous) can produce undesirable glitches (毛刺) on the decoding output.

One way to eliminate the glitches is strobing (选通), which enables the decoded outputs at time after the glitches have a time to disappear.

若 CLK=HIGH,则忽略,有效电平出现的会晚一些。

Counter Applications (计数器应用)

A Digital Clock.

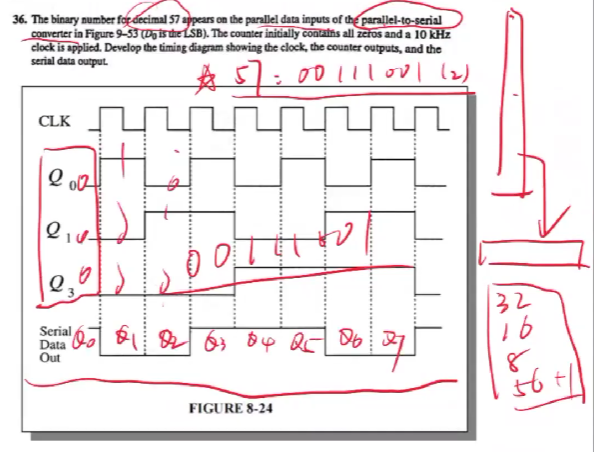

Parallel-to-Serial Conversion